发布日期:2024-08-25 23:04 点击次数:80

自出身以来,BCD 时间就充分运用了两种主要时间(多晶硅栅极 CMOS 和 DMOS 电源架构)在归并芯片上的集成。它与双极元件的兼容性使得八成创建将数字和模拟支配与高效电源经管部分相无间的 SoC(片上系统)。BCD 工艺的生成基于 CMOS 基线和新光刻节点的几何缩放章程,以终了总计集胜仗能的面积和资本的总体镌汰。从历史上看,BCD 时间平台的发展受到重要应用边界的鼓励,举例用于狡计的硬盘驱动器和用于工业应用的怒放支配。

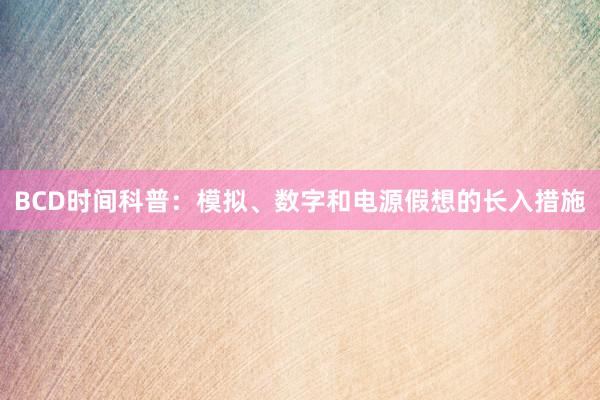

BCD(双极 CMOS DMOS)是一种用于驱动高压元件的工艺,等闲应用于音频放大器、RF(射频)和汽车工业等各式应用。它是电源 IC 的一项重要时间。该工艺触及用于精准模拟功能的双极、用于数字假想的 CMOS 和用于电源和高压的 DMOS。这意味着单个芯片具有图 1.1 所示的三种功能。这三个功能部分的假想具有不同的开发和优化圭臬。

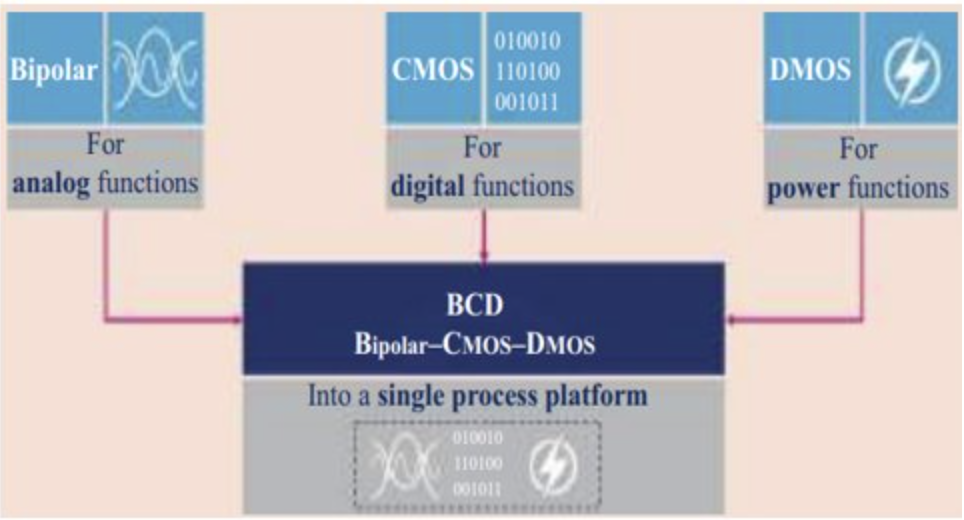

商酌词,它们的集成关于终了正确的系统功能至关紧迫。每个部分齐无法镇定终了系统的预期缱绻。它们必须协同责任智商提供所需的合座功能。为了终了最好性能并最大支配地减少由于耗散而产生的自热,紧迫的是将不同部分尽可能围聚相互。这种接近性不错减少寄奏效应,最大支配地减少信号延迟,并通过允许通盘芯片高效散热来增强热经管,如图 1.2 所示。

BCD(双极 CMOS DMOS)

典型的 BCD 时间在归并工艺中提供低压逻辑 CMOS 晶体管、高压晶体管、二极管、电阻器和 MIM 电容器。BCD 工艺具有寄生双极晶体管,特殊恰当制作带隙基准等模拟电路。

图 1.1

图 1.2

使用BCD时间的优点:

进步系统可靠性

减少电磁打扰

更小的芯单方面积

高动力服从

BCD时间架构

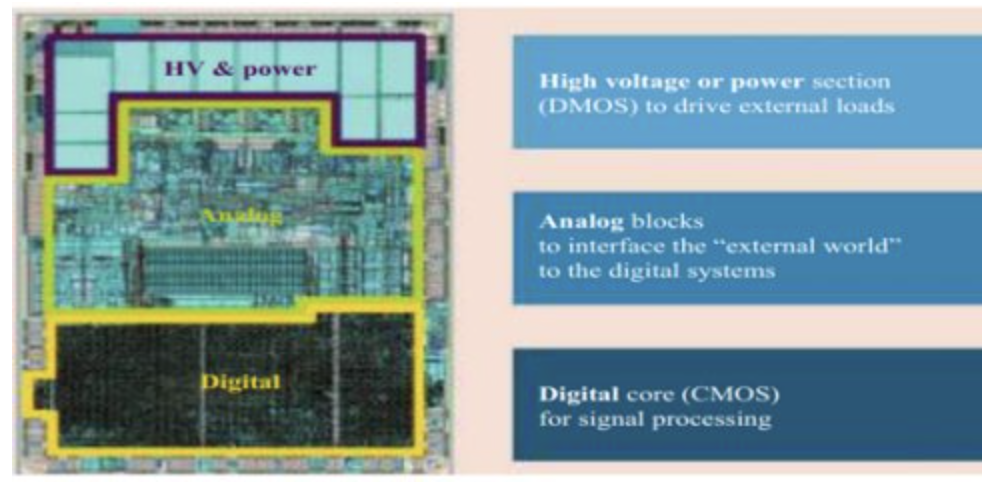

图 2.1

C- 集电极,B- 基极,E- 辐照极,S – 源极,G – 栅极,D – 漏极,B – 推行

上图2.1给出了典型的BCD时间架构。

上图3.1自满了BCD时间工艺历程。

BCD工艺历程笼统:

从块状基底开动:

厚硅晶片。

广泛掺杂 p 型杂质。

外延千里积:

基板上滋长一层薄薄的略带 p 掺杂的硅层。

使用外延(epi)千里积时间。

外延层的用途:

手脚后续制造要领的起初。

关于半导体器件制造至关紧迫。

掺杂水平研究(均衡掺杂水平):

基板电阻:

它不应太低,以幸免基板中的电阻过大而损害器件性能。

硅的晶体结构不应太高,因为它不错确保制造的器件具有精良的电气性能和可靠性。

该工艺历程从块状衬底开动,块状衬底是一块掺杂广泛 p 型杂质的厚硅晶片。

当电流注入衬底时,衬底电阻越小,噪声越低,电气相识性越高。这是因为衬底和间隔环形成的寄生双极晶体管不太可能被较大的电流触发。

保捏低衬底电阻有助于最大支配地减少寄奏效应并进步半导体器件的合座性能和可靠性。

接下来,咱们注入埋层,即通过特殊名义地注入锑(Sb)离子而创建的高度N掺杂区域。

随后,在埋层上方滋长出新的 P 型外延层来容纳有源区。

然后实施深沟槽间隔,以终了芯片不同部分之间的横向间隔,其中性能和噪声扼制至关紧迫。该时间触及在基板上蚀刻深沟槽并用二氧化硅 (SiO2) 等介电材料填充。

深沟槽间隔可灵验间隔半导体器件的有源区,从而减少串扰、走电流和其他可能镌汰性能并加多噪声的无益相互作用。这种间隔时间在高性能集成电路中尤为紧迫,因为精准支配电气间隔关于终了最好功能至关紧迫。

随后,为集成电路界说有源区。笔据时间节点和特定假想章程,半导体晶圆上的有源区不错分派给单个器件或多个器件。这种分派取决于各式身分,举例所需的电路功能、布局抑制以及假想所需的集成度。

在半导体假想中,退缩不同有源区域之间的电流流动至关紧迫。这频繁通过灵验的间隔时间来终了,举例局部氧化硅 (LOCOS) 或罗致浅沟槽间隔 (STI)。

接下来,咱们植入需要最大热预算的阱(HV 阱)。具体来说,它们是间隔阱(衬底内的间隔区域,可退缩电路不同部分之间的电气相互作用)、LD-MOSFET 的阱(n 阱或 p 阱,以优化其性能并将它们与芯片上的其他组件间隔),以及高压 n-MOS 和 p-MOS 的主体(间隔以确保正确偏置并退缩可能导致开发故障或损坏的或然电流)。

在半导体制造中,完成注入工艺后,衬底会在炉中履历热退火工艺。此退火要领关于激活注入衬底的掺杂剂以及树立注入过程中形成的晶体挫伤至关紧迫。

退火工艺频繁触及在受控环境中将晶圆加热至高温,使掺杂剂扩散到硅晶格中并形成所需的电结。这种热处理还有助于缓解晶体结构中的应力,从而进步所制造的半导体器件的合座质地和可靠性。

咱们还植入了需要最低热预算的阱(LV 阱)。植入后,基板通过快速热退火 (RTA) 进行必要的热处理。

在半导体制造中,MOSFET 晶体管的栅极氧化物是使用原位蒸汽生成 (ISSG) 工艺滋长的。该措施触及原位生成蒸汽 (H2O),频繁通过晶圆名义的氢 (H2) 与氧 (O2) 发生响应。然后使用蒸汽滋长一层薄薄的二氧化硅 (SiO2),用作栅极氧化物。

关于高压器件,当先将栅极氧化物滋长到其所需的最大厚度。随后,扩张装璜要领,其中应用掩膜来界说需要氧化物的区域。然后蚀刻掉氧化物的走漏区域,只在所需区域留住栅极氧化物。栅极氧化物不绝滋长,要点是终了所需的最终厚度。这种滋长不错笔据需要部分蔓延到高压区域,确保通盘基板的均匀性和合乎的绝缘性。

在掺杂厚的多晶硅层后,将高剂量的硼或砷注入需要创建 n+ 或 p+ 区域的特定区域。在进行金属斗殴的特定区域形成硅化物层。硅化物层的形成灵验地将半导体-金属结回荡为金属-金属结。临了一步是后端 (BEOL) 工艺,指的是触及金属互连集成的制造临了阶段。

频繁,MIM 电容用具于 BCD 时间,因为它们不错最大支配地减少寄生电容到基板。MIM 电容器最好在时间 BEOL 的上部金属层之间终了。MIM 电容器的另一个优点是它们不错堆叠在有源元件上方,与其他搞定决策比拟,不错减小芯片尺寸。

CMOS 中的 PMOS/NMOS 器件最常见的有四个端子(栅极源极漏极体),但在咱们的假想中,咱们有七个 PMOS 端子和六个 NMOS 端子器件,区别如下图 4.1 和图 4.2 所示。

咱们开发中的其他三个末端是:

DPW(深P阱) -深P阱屏蔽了包含PMOS晶体管的N阱,退缩其从外延层而不是N阱手脚电荷齐集电极齐集信号电荷。

ISO NBL(间隔 N 型埋层)——用于终了不同电压下责任的电路之间的间隔或退缩噪声通过大众 P 衬底耦合。它用作 P 衬底内的 N 型掺杂剂埋层。该层灵验地将衬底的不同区域相互间隔,退缩或然的电气相互作用并减少电路之间的噪声传播。ISO NBL 有助于最大支配地减少通过衬底的噪声耦合。

SUB ISO(间隔基板)——数字模块中的广泛开关可能会影响 RF 和模拟模块的性能,反之也是。咱们不错将电路的各个模块相互间隔,这么 RF 和数字模块之间通过基板的耦合就会最小。虽然,电源线和地线之间存在相互作用,必须单独搞定。

这种间隔使得HVNW(高压N阱)和NBL(N埋层)处于不同的电位。

DPW端子贯穿地线,NBL端子贯穿电源线,SUB端子贯穿地线。

ISO环的层信息如图5.1所示。

总计 PMOS 和 NMOS 器件簇齐遗弃在间隔环中,如下图 5.2 所示。

为了使用典型的 MOS(金属氧化物半导体)器件处理高压信号,器件端子频繁会浮动,从而八成天真地处理高压信号,同期保捏操作竣工性并退缩电气应力。在 CMOS(互补金属氧化物半导体)工艺中,基板浮动如实会镌汰性能,这主若是由于基板的电阻率较低。

为了搞定与衬底浮动有关的挑战并进步 CMOS 假想的性能,罗致了三阱结构。该结构灵验地将晶体管主体和深 N 阱与衬底间隔,从而终了单独偏置。由于寄生电容和其他身分,间隔服从会随频率而变化。在低频下,间隔频繁很灵验,因为间隔区域(举例深 N 阱和衬底之间)之间的关态电阻很高。这种高电阻可最大支配地减少走电流并退缩不同区域之间的信号径直耦合。